| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| |

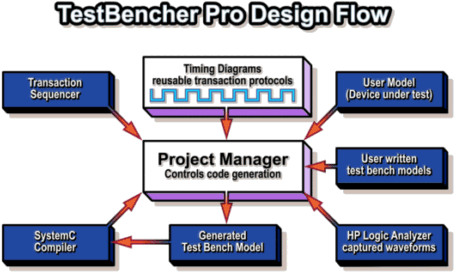

TestBencher Pro generates SystemC CodeBLACKSBURG, VA, March 15, 2001 - SynaptiCAD Inc., the design technology leader for timing diagram editing and test bench generation, today announced the release of TestBencher Pro v7.2, which supports graphical code generation for the SystemC language. TestBencher Pro provides designers with a graphical environment for generating cycle-based bus-functional models from language-independent timing diagrams. TestBencher Pro generates all of the class code for each diagram including the port mappings and sensitivity lists, as well as the top-level code for interfacing to the SystemC simulator. "We welcome SynaptiCAD's use and leverage of SystemC," says Kevin Kranen, Co-chair of the SystemC Steering Group. "It's encouraging to see growing support from EDA companies, like SynaptiCAD, which further endorses this growing system-level standard." "SystemC is a powerful language for very high level modeling of digital systems," said Dan Notestein, president of SynaptiCAD. "By combining TestBencher Pro's rapid prototyping environment with SystemC's modeling capabilities, designers can rapidly examine system tradeoffs during the early stages of their design before they commit to implementing a given hardware architecture."

About TestBencher ProTestBencher Pro generates SystemC test benches directly from timing diagrams using a bus functional approach to test bench designs. Bus-functional models execute faster than complete functional models and can be created from data contained in data sheets. A bus-functional model is also easier to maintain and debug than raw test vector data. Additionally, TestBencher's graphical representations and automatic code generation abstract coding details away from the user. This abstraction reduces the amount of time needed for test bench generation. Automating the most tedious aspects of test bench development allows engineers to focus on the design and operation of the test bench rather than the painstaking aspects of code development. TestBencher Pro can also generate VHDL and Verilog test benches from the same diagrams used to generate SystemC code. TestBencher Pro features state and timing protocol checker generation for verifying the response of the model being tested. TestBencher's "sampling" construct can check the state of a signal at a given point in time or over a window of time, and samples can also check for either a state change or for stability during the sampling window which is specified as a number of clock cycles. TestBencher also supports "sequence recognition", which allows a sequence of states to be defined for a timing diagram and have the generated test bench "trigger" off that sequence whenever it occurs during a simulation. This feature can be used to verify that the sequence occurred, verify a set of timing requirements whenever that sequence occurs, or stimulate the design in a certain way whenever that sequence occurs. This technique is particularly useful when generating bus-functional models for "slave" devices which are designed to respond in a certain way whenever they are selected by a "bus master" device. Other features include automatic port and signal extraction from HDL models, parameterization of both state and timing values through function call parameters or data files, conditional application of edge transitions, burst transactions, data source/target support for files, queues, and arrays. SynaptiCAD also offers a complete line of VHDL and Verilog model generation, simulation, and timing diagram visualization tools including: VeriLogger Pro - Verilog simulator, WaveFormer Pro - waveform translator, Timing Diagrammer Pro - timing diagram editor, and DataSheet Pro - a Data Book design tool. |

| |