| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| |

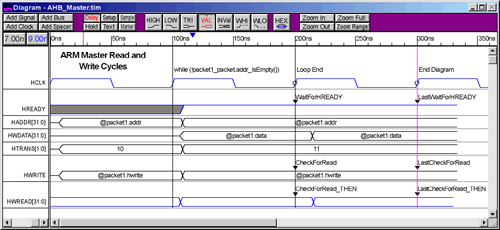

| Von Donna Mitchell, erschienen in ElektronikPraxis, Februar 2002 Testbench grafisch generierenDie grafische Code-Generierung von SynaptiCAD ermöglicht die sprachenunabhängige Testbench-Entwicklung, um geeignete Testbenches schnell, klarund präzise zu beschreiben. Das Entwickeln von Testbenches in einer Sprache wie VHDL oder SystemC zum Stimulieren von HDL-Designs und Überprüfen der Ausgangssignale ist eine der zeitaufwändigsten Aufgaben in der heutigen digitalen Schaltungsentwicklung. Dies liegt daran, dass Testbenches typischerweise ein viel größeres System als das vom Entwickler entworfene modellieren. Des weiteren werden Testbenches in der Regel unter Benutzung von Verhaltenskonstrukten modelliert und der Code ist anfällig gegen Race-Conditions, die zu unerwartetem Laufzeitverhalten führen. Grafische Code-Generierung bietet eine sprachunabhängige Lösung zur Testbench- Entwicklung, die es Ingenieuren erlaubt, Testbenches schnell und in einer klaren und präzisen Art und Weise zu beschreiben. Die grafische Testbench-Erzeugung ist das automatische Gererieren von Quellcode. Das Programmpaket TestBencher Pro von SynaptiCAD hat eine intuitiv zu bedienende Grafikoberfläche, mit der sich auch komplexe Bustransaktionen und Schnittstellenbeschreibungen modellieren lassen. Pipelining, Split-Phase- Transaktionen, Datenstrukturen und Speicher sowie Sequenzerkennung sind modellierbar. Das Tool verwendet Timing-Diagramme, um Bus-Transactor-Quellcode in der vom Anwender bevorzugten Sprache zu generieren. Grafikdarstellung erleichtert die ZusammenarbeitAus den grafisch dargestellten Timing-Diagrammen produziert die Software wahlweise Testbenches in VHDL, Verilog, SystemC, OpenVera oder e. Mittels Diagrammen kann der Ingenieur auf hoher Abstraktionsebene arbeiten und Low-Level-Coding-Probleme dem Werkzeug überlassen. Testbench-Code ist trotz modularer Programmiertechnik häufig schwer zu verstehen, weil in einer Testbench eine hohe Zahl parallel ablaufender Vorgänge vorhanden sein kann. Timing-Diagramme ermöglichen eine weitaus klarere, knappere und leichter verständliche Beschreibung der Signalaktivitäten und Interaktionen zwischen Prozessen. Die grafische Darstellung in solchen Diagrammen erleichtert die Zusammenarbeit mehrerer Designer an einer Testbench. Grafik: Ein Timingdiagramm, das den Testbenchcode f�r einen AMBA pipelined Bus Master generiert. AutorDonna Mitchell ist Vice President f�r Strategisches Marketing bei SynaptiCAD Inc. Sie erlangte ihren Bachelors- und Masters-Degree in Electrical Engineering an der Virginia Tech Universit�t. Mitchell ist eine der zwei Gr�nder von SynaptiCAD Inc. Graphical Test Bench Generationby Donna Mitchell, Appeared in ElektronikPraxis, February 2002 Developing test benches to stimulate HDL designs and check their output is one of the most time consuming tasks in modern digital design. This is because test benches typically model a much larger system than the one that the user is designing. Also, test benches are generally modeled using behavioral constructs and the code is prone to race conditions that lead to unexpected run time behavior. Graphical code generation offers a language independent solution to test bench development that enables engineers to quickly describe test benches in a manner that is clear and precise. Graphical test bench generation is the process of automatically creating test bench source code from an interface description based on graphical timing diagrams. SynaptiCAD has developed TestBencher Pro, a simple and intuitive graphical test bench generator that can be used to model very advanced bus transactions and interface descriptions. Pipelining, split-phase transactions, data structures and memories, and sequence recognition can all be modeled. TestBencher uses timing diagrams to generate bus transactor source code in the user's preferred verification language: VHDL, Verilog, SystemC, OpenVera, or "e". By using timing diagrams, the engineer can work at a high level of abstraction, leaving the tool to deal with low level coding issues like race conditions. Test bench code is often difficult to understand even when written using modular programming techniques because of the large amount of parallel activity occurring in the test bench. Timing diagrams allow a much clearer and concise description of the interaction of parallel processes and signal activity. A graphical representation also facilitates the collaboration of many engineers on a single test bench by removing the need to interpret source code. Any engineer familiar with the design specifications is able to look at a given timing diagram and have an immediate understanding of what the transactor does, dramatically simplifying test bench maintenance. Figure: A timing diagram that generates the test bench code for an AMBA pipelined bus master driven by queue data structure AuthorDonna Mitchell is Vice President of Strategic Marketing at SynaptiCAD Inc. She received her BS and MS degrees in electrical engineering from Virginia Tech. Mitchell is one of the two founders of SynaptiCAD Inc. |

| |