| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| |

| |

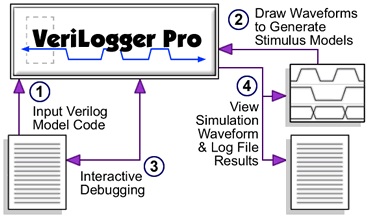

Verilog Simulator with Graphical Test Vector GenerationVeriLogger Pro, by SynaptiCAD is a complete design and verification environment for ASIC and FPGA designers. It contains a new type of Verilog simulation environment that combines all the features of a traditional Verilog simulator with the most powerful graphical test vector generator on the planet. Model testing is so fast in VeriLogger Pro that you can perform true bottom-up testing of every model in your design, a critical step often skipped in the race to market. Test vectors can be imported or exported from HP logic analyzers, pattern generators, and 3rd party VHDL, Verilog, and SPICE simulators for reuse. Simulation features include waveform viewing, optimized gate-level simulation, single-step debugging, point-and-click breakpoints, hierarchical browser for project management, and batch execution. Customer Feedback

Watch an Animated Tutorial of Verilogger ProTechnical Details

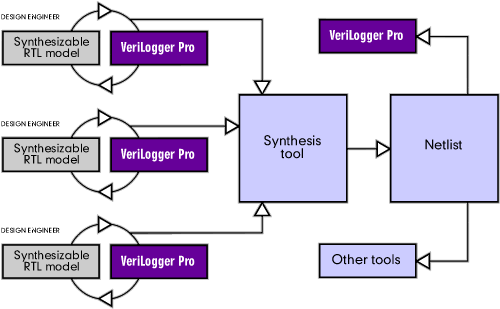

Evaluate and Purchase VeriLogger:Complete ASIC and FPGA design Environment In a typical design of a large ASIC, each contributing engineer can use a VeriLogger to develop and simulate their portion of the chip. After each portion has been synthesized and checked, the entire integrated design can be rapidly simulated and verified using VeriLogger with its optimized gate level simulation engine activated. VeriLogger interfaces to synthesis tools, place-and-route tools, and all vendor Verilog libraries. VeriLogger supports design flows using Actel, Altera, Lattice, Lucent, Quicklogic, Vantis , and Xilinx devices including full timing verification. Graphical Test Bench GenerationVeriLogger can automatically generate test bench code for your design models. Using the built-in timing diagram editor, just draw the stimulus waveforms and VeriLogger will write the test bench and simulate it with your design models. VeriLogger also includes an instant-feedback simulation mode in which any change to the design code or the waveform stimulus vectors results in an automatic re-simulation. This mode is especially useful for quickly verifying the functionality of small design blocks, making it possible to perform true unit-level testing of designs. Cut your Design Costs by a Factor of 10If you've wanted to move up to the latest design methodologies, but have hesitated because of the high entry costs, VeriLogger is your answer. If you've already moved to Verilog, but haven't been able to afford to equip all the members of your team with their own simulators, VeriLogger is your answer too. VeriLogger is 100% compatible with Verilog-XL and integrates seamlessly into an XL environment. Got a question about VeriLogger Pro and HDLs?Post your question on the newsgroup comp.lang.verilog and it will be answered by our technical support staff (the newsgroup is checked at least once a day). You can always call 800-804-7073 to have any questions answered directly. |

| |