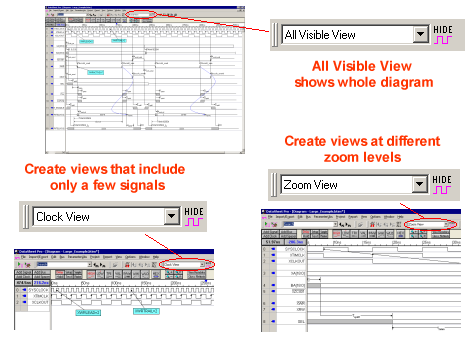

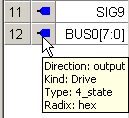

| New Features in SynaptiCAD Tool Suite v14.0 The Timing Diagram editors: Timing Diagrammer Pro, WaveFormer Pro, DataSheet Pro - In DataSheet Pro, a new Update View button allows new signals and parameters to be added to an existing view. This feature is also supported in BugHunter Pro.

- For DataSheet Pro there is also improved image view printing from the print dialog.

- For DataSheet Pro and other editors with the OLE option, we have improved the OLE linking support, and the OLE image generation now supports views.

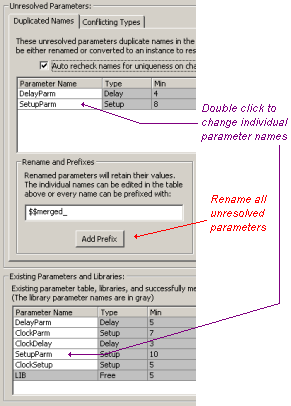

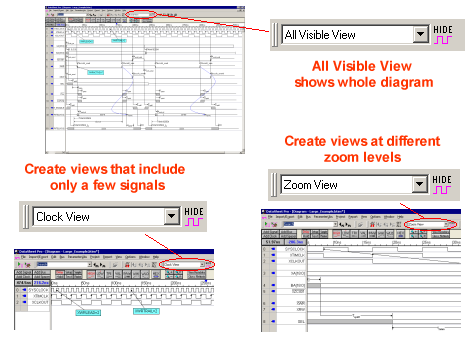

- The Duplicated Parameter Names dialog opens when a name or type conflict is found during a diagram merge or parameter renaming operation. Conflicts can be resolved by either renaming to create a new parameter or by converting to an existing parameter. See Section 10.4 Merging Diagrams for more information.

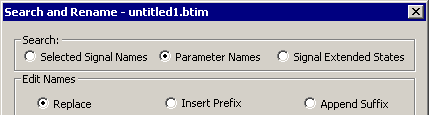

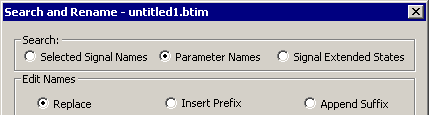

- Search and Rename function for replacing parameter names is now linked into the Duplicated Parameter Names dialog to help prevent the loss of data if duplicate parameter names are created by the rename operation.

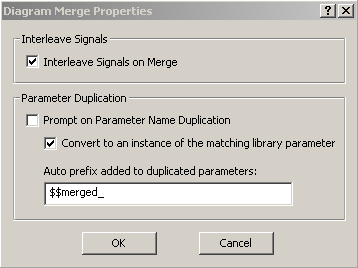

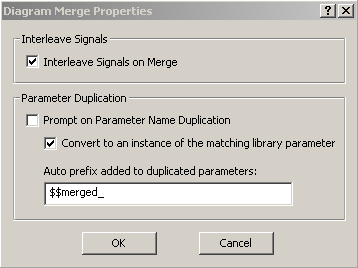

- The new Diagram Merge Properties dialog controls how signals are grouped after the merging of two diagrams. It also controls how duplicate parameter errors are handled, this is especially useful for batch processing of the merge diagrams.

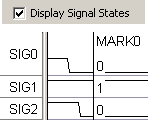

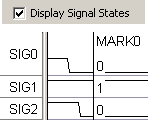

- Display Signal States with a Marker as shown in Section 6.5: Marker Lines. Markers can permanently display the signal state values if the Display Signal States box is checked in the Marker Properties dialog. Otherwise the signal states are only shown when the mouse hovers over the marker line.

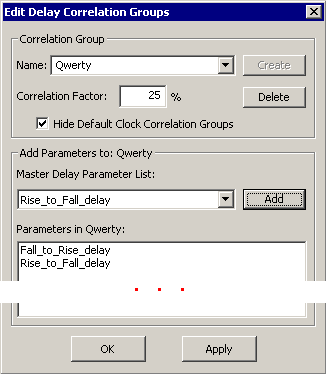

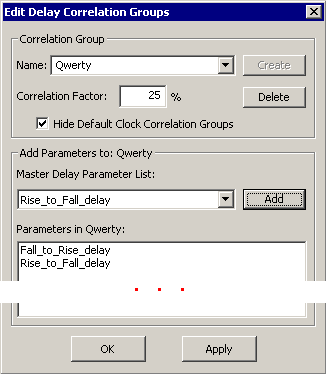

- The Edit Delay Correlation Groups dialog has been rearranged to provide more room for delay names and a new Apply button was added. See Section 5.1: Delays to learn more about how you can design faster circuits using the Delay Correlation features. Even though data sheets for IC's list large min/max uncertainty ranges for each delay, the delays within any particular IC will be much more tightly grouped. To take advantage of this, delays from a particular IC can be added to a correlation group. The editor will then recalculate the setup and hold times so that faster circuits can be designed. When a delay is added to a correlation group, all timing calculations are automatically updated accordingly.

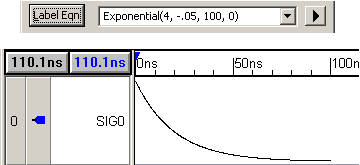

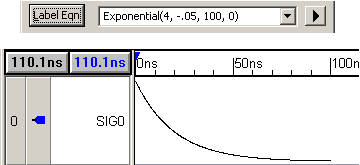

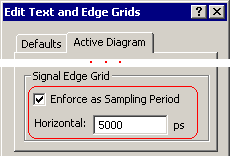

- The Exponential label equation draws a waveform with an exponential curve. You have control over the amplitude, exponent value, duration, and the starting offset.

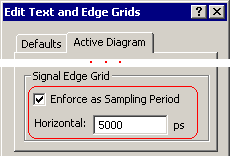

- Normally, the analog label equations auto-select a sampling period that will result in a smooth curve. This often results in a waveform with a lot of points very close together. Now you can specify a user-defined sampling period for all waveforms generated via analog equations.

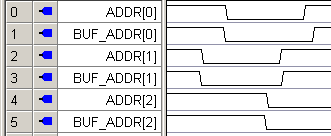

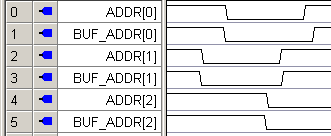

- Signals can be sorted by bit significance so that individual bits from two or more buses can be easily compared to each other.

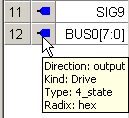

- To quickly view a signal's properties, let the mouse hover over the direction column and a tooltip will appear. Hovering over the signal name will show a tooltip of the full signal name (this is handy for signals with long names).

- Xilinx's place and route tool creates *.twx files which contain timing path delays through the FPGA. Timing parameter values can now be imported directly from these files so that you can analyze the timing paths through your post-layout design.

- Speeded up hiding signals in very large diagrams (e.g. files with hundreds of thousands of signals).

- Optimized memory usage to enable loading diagrams with over a million signals (with the GigaWave feature).

- Faster drawing of signals in the diagram window with large numbers of signals or many waveform events.

- Improved group bus event handling so buses are faster and more robust.

- Faster timing evaluation of complex diagrams with many timing parameters.

- To draw consecutive segments of the same waveform type, double click on a state button to set it as both the next state and the toggle state.

- When multiple diagrams are open, the parameter table automatically changes tabs to show parameters for the active timing diagram window.

- TDML now supports non-ASCII characters (e.g EU and Japanese characters)

V2V - Verilog-to-VHDL and VHDL-to-Verilog model translation - Added support for processing attributes in Verilog.

- Added support for the `undef directive

- Added support for the `line directive

- Ability to enable/disable options in the V2V translation dialog via drag and drop operations.

TestBencher Pro - Better searching inside the hierarchical testbench project tree.

VeriLogger Extreme - VeriLogger Extreme now supports encrypted models.

- VeriLogger Extreme also supports binary SmartModels available from many FPGA/ASIC vendors.

- Verilog 2001 Constant Functions are supported.

- Full support for TF and VPI functions.

- Faster simulation build/rebuild times, startup times, and simulation runtimes.

- New compilation system eliminates repeated firewall warnings.

- Gates-on-the-Fly (GOF) graphically analyzes and edits large Verilog netlists that have been generated from a synthesis or layout tool. Several of SynaptiCAD's products contain a waveform viewer that can be used with GOF to display VCD waveforms (cross-probing) and send logic state values to GofTrace Schematic windows.

- Right clicking on the timeline of the timing diagram window sends signal states at that time to GOF.

- In GOF, the Annotate Schematic setting causes the signal states to be displayed on the pins of the gates. The next and previous buttons move the simulation time backward and forward.

BugHunter Pro - The Show Drivers menu opens a window that shows all the drivers for a net. See the BugHunter and VeriLogger Manual in Section 2.5: Find Drivers.

- Easier to rapidly delete multiple breakpoints in BugHunter.

- Updated support for latest version of VeriLogger Extreme, ActiveHDL, and ncsim.

- Each simulator stores it's own console history to simplify switching back and forth between different simulators. See the BugHunter and VeriLogger Manual in Section 2.7: Command Console for Interactive Debugging.

- Library directory paths now work even with compiled-code simulators that don't natively support a -y option. See the BugHunter and Verilog Manual in Step 2: Setup the Project Simulation Options.

New Platform support - 64 bit Linux

- Minor fixes for Vista

New Features pages for previous versions: List of Features in Version 13.0 List of Features in Version 12.0 List of Features in Version 11.0 |